# Static modeling of fully-printed OTFTs using a modified Amorphous-Si: H TFT model

M. A. Sankhare<sup>1</sup>, E. Bergeret<sup>1</sup>, P. Pannier<sup>1</sup>, R. Coppard<sup>2</sup>

<sup>1</sup>IM2NP (UMR 7334), Campus de Saint-Jérôme, Avenue Escadrille Normandie Niémen - Case 142, F-13397, France <sup>2</sup>Laboratoire des Composants Imprimés, LITEN-LCEI, CEA-Grenoble, France

# ABSTRACT

The presented work contributes on the modeling of low cost fully-printed Organic Thin Film Transistors (OTFTs). Due to the lack of OTFTs' models included in industrial and commercial Computer Aided Design (CAD) tools, the Amorphous-Si: H TFT model presents in most CAD tools and initially planned for Amorphous Silicium Hydrogenated Thin Film Transistors (A-Si: H TFTs) was used. In the paper, the parameter-extraction procedure was done using a specific approach based on an iterative method which improves processing time and precision. This allows taking into account the series resistance of the designed OTFTs generally neglected for A-Si: H TFTs. In addition, some parameters appeared to be dependent on the OTFTs' geometry. These geometry dependences allowed the setting up and the creation of a single model valid for a wide range of geometries. The proposed model offers a possibility to design rapidly complex system with more than one hundred OTFTs on flexible plastic foils. It passed all stages of validations in static, and the measurements of some basic circuits were compared with simulation results.

Keywords: A-Si: H TFT, modeling, OTFTs, iterative extraction, geometry dependence.

# 1. INTRODUCTION

Organic electronics is currently the subject of intense research for several reasons. It is based on materials called conductive polymers or small molecules which require low-cost manufacturing processes and no huge-controlled environment. These low temperature techniques present the advantage of being compatible with flexible substrates like plastics or papers. Due to these advantages, the use of organic electronics is interesting in many applications like for OTFTs manufacturing [1], OLED or solar cells [2] fabrication. Even if the performances of organic components do not match those of inorganic ones,—generally due to the weak mobilities [3], [4] or the high series resistance [5]–[7] — many works recently reported show that some basic [8]–[12] or complex [13]–[15] circuits can be designed. However, to exploit all the possibilities of organic devices and to test their limits, precise models should be available, this will help to predict behavior of the designed circuits.

Although the modeling of OTFTs has been the focus of many papers, most of the proposed models are not scalable [3], [6], [16], and do not include either all stages of model validations [6] or series resistance extractions [17], [18]. In this paper, the Amorphous-Si: H TFT model developed at Rensselaer Polytechnic Institute (RPI) is used. It is present in all modern simulators and allows simulation of complex circuits rapidly. However, the physical phenomena in organic devices are not entirely similar to the ones in amorphous devices then the Amorphous-Si: H TFT model cannot be applied directly to OTFTs and needs modification to integrate the specific geometry dependences of OTFTs parameters. Moreover, the series resistance generally neglected for A-Si: H TFTs should be taken into account in case of OTFTs. The thus-modified Amorphous-Si: H TFT model considering theses dependences proved performant for a large range of geometries.

The paper is divided into six sections. Section 2 is about the OTFT modeling in above-threshold regime and briefly presents the extraction methods. Section 3 presents the iterative extraction procedure applied to OTFTs. In Section 4, the proposed scalable model based on the geometry dependences of extracted parameters is presented. Section 5 focus on the model validation and the last section, with a benchmarking from literature, concludes the paper and announces future works.

#### International Journal of Enhanced Research in Science, Technology & Engineering ISSN: 2319-7463, Vol. 4 Issue 10, October -2015

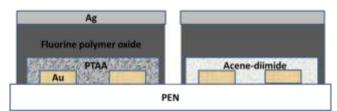

The OTFTs manufacturing in the presented work is as follows: over an insulating Polyethylene Naphtalate (PEN) substrate metalized with a 30nm-thick gold (Au) layer, the drain and source electrodes are created by laser ablation. After this, a 100nm-thick organic semiconductor (OSC) layer is deposited by screen printing. The P- and N-type organic semiconductors used are respectively the Polytriarylamine (PTAA) and the Acene-based-diimide. Then, an 800nm-thick dielectric layer (the fluorine polymer oxide) is also formed by screen printing. Finally, a 5 $\mu$ m-thick Ag layer is deposited to form the gate electrode, and a final annealing at 100°C is achieved. The schematic cross section of the designed OTFTs is presented in Fig.1

Figure 1. Schematic cross section of the presented OTFTs (top gate/ bottom contact configuration)

## 2. MODELING IN ABOVE-THRESHOLD REGIME

The UMEM (Unified Model and Extraction Method) approach was used for the parameter extraction. This method allowed the individually extraction of each parameter following a specific order. The main parameters were extracted from the OTFTs' transfer and output characteristics, using the same extraction procedure as in [19], [20] applied on A-Si: H TFTs. Thus, the parameters Gamma ( $\gamma$ ), the threshold voltage (V<sub>T</sub>), the band mobility ( $\mu_0$ ), the characteristic field voltage (V<sub>aa</sub>) and the series resistance (R) were extracted in linear regime (low drain-source voltage) using the H function defined in (3). And, the saturation parameters like the saturation modulation parameter ( $\alpha_{sat}$ ), the channel-length modulation ( $\lambda_{sat}$ ) and the knee-parameter (M) were extracted in saturation regime (high drain-source voltage). In linear regime, the current could have been approximated following (1) where W and L are the OTFT dimensions, then, the H function could be rewritten following (4).

$$I_{dslin} = \frac{K^* \mu_0 * (V_{gs} - V_T)^{1+\gamma}}{V_{aa}^{\gamma} + R^* \mu_0 * K^* (V_{gs} - V_T)^{1+\gamma}} * V_{ds}$$

(1)

$$K = \frac{C_{ox} * W}{L} \tag{2}$$

$$H(V_{gs}) = \frac{\int_{0}^{V_{gs}} I_{ds}(x) dx}{I_{+}(V_{-})}$$

(3)

$$H(V_{gs}) = \frac{1}{\gamma + 2} * (V_{gs} - V_T + R * I_{dslin})$$

(4)

The mobility model is expressed in (5). Equation (1) associated to (5) allow rewriting the mobility in linear regime following (6).

$$\mu_{fet}(V_{gs}) = \mu_0 * \left(\frac{V_{gs} - V_T}{V_{aa}}\right)^{\gamma}$$

(5)

$$\mu_{fet}(V_{gs}) = \frac{I_{dslin}}{K^* (V_{gs} - V_T) (V_{ds} - R^* I_{dslin})}$$

(6)

# 3. OTFT-SPECIFIC EXTRACTION

#### A. Discussion about series resistance

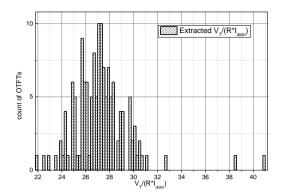

In case of A-Si: H TFTs, the threshold voltage is extracted by only considering the intercept of the H function because the term  $R^*I_{dslin}$  is considered negligible compared with  $V_T$  [18],[20]. With the presented OTFTs, the mean value of the ratio  $V_T/R^*I_{dslin}$  on a sample of 144 N-OTFTs was 27 as shown on the statistical graph in Fig.2 meaning that the term  $R^*I_{dslin}$  is only 3.7% (1/27) of  $V_T$ . This result shows that the term  $R^*I_{dslin}$  could be neglected in the calculation of the H function, but, it will be shown in the following sub-section that the series resistance could not be neglected during the parameter extraction procedure. The series resistance were calculated using (7) deduced from (1).

$$R = \frac{V_{ds}}{I_{dslin}} - \frac{V_{aa}^{\gamma}}{K * \mu_0 * (V_{gs} - V_T)^{1+\gamma}}$$

(7)

# Figure 2. Dispersion of extracted V<sub>T</sub>/R\*I<sub>dslin</sub> ratio on a sample of 144 Acene-based diimide N-OTFTs

## B. Iterative method for the above-threshold parameters extraction and validation procedure

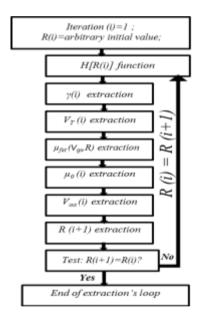

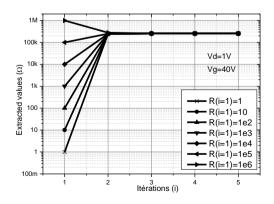

An iterative method which improves precision and respects the UMEM method was developed as shown in Fig.3. For the extraction method to be valid, reproducibility was tested using different initial values of series resistance, and only a few iterations were necessary to converge to the same value, thus confirming to be independent of the initial value and confirming reproducibility as shown in Fig.4. The iterative extraction method presented in Fig.3 were first applied to one transistor and the results are presented in table 1 showing the impact of series resistance on  $\gamma$ , V<sub>T</sub>,  $\mu_0$  and V<sub>aa</sub> parameters.

Figure 4. Convergence of extracted series resistance for different initial values, Acene-based diimide N-OTFT, W/L=50, T=25 $^{\circ}$ C

Table 1: Extracted above-threshold parameters for an Acene-based diimide N-OTFT, W/L=1000 $\mu$ m/20 $\mu$ m, (T=25°C).

| Parameters                | Neglecting R | Considering R |  |

|---------------------------|--------------|---------------|--|

| Itérations                | 1            | 4             |  |

| γ                         | 1.64         | 2.16          |  |

| VT                        | 4.64         | 4.45          |  |

| µ0 (cm <sup>2</sup> /V.s) | 0.32         | 1.1           |  |

| Vaa(V)                    | 27           | 56            |  |

| R (kΩ)                    | 0            | 256           |  |

| asat                      | 0.16         | 0.16          |  |

| λsat (1/V)                | 0.00176      | 0.0017        |  |

| Μ                         | 2.25         | 2.25          |  |

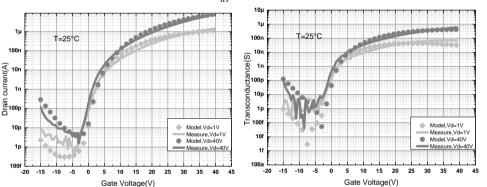

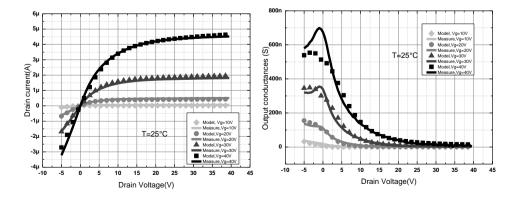

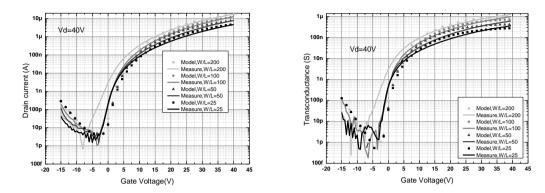

## C. Complete model for all regimess

Although in similar works, recent methods of modeling the sub-threshold and leakage regimes [21], [22] was proved to be very efficient for OTFTs, here, the modeling of the sub-threshold- and leakage-regimes was done using the same expression than in Amorphous-Si: H TFT model by extracting  $V_{dsl}$ ,  $E_l$ ,  $I_{ol}$ ,  $V_{gsl}$ ,  $\delta_0$ ,  $V_{min}$  and Delta parameters. The parameters related on table 1 (considering R) were thus associated to these parameters. Comparisons between modelled and measured characteristics showed correct agreement as shown in Fig.5 and Fig.6. The figures showed also correct agreement in the sub-threshold- and leakage regimes and for the current derivatives (8), (9).

$$G_m = \frac{dI_{ds}}{dV_{es}} \tag{8}$$

$$G_d = \frac{dI_{ds}}{dV_{ds}} \tag{9}$$

Figure 5. Modelled (dotted) and measured (lines) characteristics (lines) for different V<sub>g</sub> bias, W/L=50, Acenebased diimide N-OTFT

Figure 6. Modelled (dotted) and measured (lines) characteristics for different V<sub>d</sub> bias, W/L=50, Acene-based diimide N-OTFT

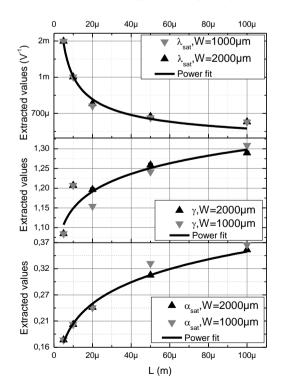

#### 4. Geometry dependences of extracted parameters

Once the improved extraction procedure validated, the extraction were thus applied to a same sample of 144 N-OTFTs. Only transistors with a same numbers of fingers were studied here. For N-OTFTs having the same dimensions, the extracted values for each parameter were averaged. The objective was to find out whether some parameters are dependent on the OTFT geometry. This was not obvious for small lengths and small W/L ratios, as the process scattering were important for small OTFT sizes and caused a lot of fluctuation, —leading us to consider only W/L ratios between 12,5 and 400. M, V<sub>T</sub> and V<sub>aa</sub> parameters did not appear to be geometry-dependent, thus being considered as process-flow-dependent parameters for which a mean value could be considered for the model. However, others parameters like  $\gamma$ ,  $\mu_0$ ,  $\lambda_{sat}$ ,  $\alpha_{sat}$  and R appear to be geometry-dependent.

#### D. L-dependence

Reséndiz *et al* [20] tried to find out the effect of length variation on transistor's parameter. He worked on A-Si: H TFTs with channel lengths ranging from  $4\mu m$  to  $12\mu m$ . He showed that reducing the transistors' lengths also reduced extracted  $\gamma$  values. Similar results to Reséndiz were found here as shown in Fig.7 and the dependence could be written as follows where  $\gamma_0$  and  $B_{\gamma}$  values were extraction-determined constants.

$$\gamma(L) = \gamma_0 * (L)^{B_{\gamma}} \tag{10}$$

The found dependence of  $\alpha_{sat}$  goes in the same way of  $\gamma$  dependence as shown in Fig.7. A physical explication of this result not yet found, further investigation must be done.  $\alpha_{sat}$  dependence could be written as follows where  $\alpha_0$  and  $B_{\alpha}$  were extraction-determined constants.

$$\alpha_{sat}(L) = \alpha_0 * (L)^{B_{\alpha}}$$

<sup>(11)</sup>

For  $\lambda_{sat}$ , the extracted values were inversely proportional to length variation following a power law (12) where  $\lambda_0$  and  $B_{\lambda}$  are also extraction-determined constants as represented in Fig.7. The found dependence is similar to the same dependence on MOS (Metal Oxide Semiconductor) crystalline transistor: indeed, due to short channel effects changing the physical properties of the transistor, the channel length modulation parameter is higher for short channel-lengths creating higher early voltage. Haddock *et al* [23] found the same progression of  $\lambda_{sat}$  in length variation when studying the short channel effects in OTFTs.

$$\lambda_{sat}(L) = \lambda_0 * (L)^{B_{\lambda}}$$

(12)

Figure 7. Dependences of extracted  $\lambda_{sat}$ ,  $\gamma$  and  $\alpha_{sat}$  on length variation, Acene-based diimide N-OTFT, T=25°C

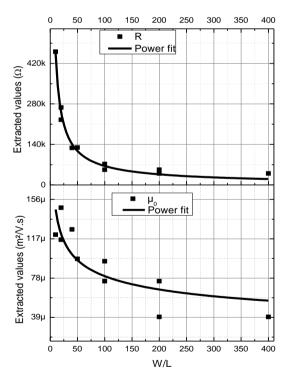

## E. W/L-dependence

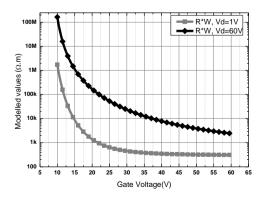

Based on the Amorphous-Si: H TFT model, the W/L ratio is related to the above-threshold current following (13). This dependence initially planned for A-Si: H TFTs was not adequate to the designed OTFTs. To try and understand this phenomenon, we investigated the geometry dependences of R and  $\mu_0$ , and found a W/L-dependence following (17) and (18) where  $\mu_{scal}$ ,  $A_{\mu 0}$ ,  $R_{scal}$  and  $A_R$  were extraction-determined constants. These dependences are represented in Fig.8.

$$I_{ds} = \frac{\left(\frac{W}{L}\right) * Cst_1}{1 + \left(\frac{W}{L}\right) * Cst_2}$$

(13)

$$Cst_{1} = C_{ox} * \mu_{fet} (V_{gs}) * (V_{gs} - V_{T}) * (1 + \lambda_{sat} * V_{ds}) * V_{ds} * \frac{1}{\left[1 + \left(\frac{V_{ds}}{V_{dsSat}}\right)^{M}\right]^{1/M}}$$

(14)

$$Cst_2 = C_{ox} * R * \mu_{fet}(V_{gs}) * (V_{gs} - V_T)$$

(15)

$$V_{dsSat} = \alpha_{sat} (V_{gs} - V_T) \tag{16}$$

$$\mu_0 \left(\frac{W}{L}\right) = \mu_{scal} * \left(\frac{W}{L}\right)^{A_{\mu_0}} \tag{17}$$

$$R\left(\frac{W}{L}\right) = R_{scal} * \left(\frac{W}{L}\right)^{A_R}$$

(18)

Figure 8. Dependences of extracted  $\mu_0$  and R on W/L ratios, Acene-based diimide N-OTFT, T=25°C

Using (5), (10) and (17), the proposed field effect mobility for the OTFTs could then be written as follows.

$$\mu_{fet^{scal}}\left(V_{gs}, L, \frac{W}{L}\right) = \mu_{scal} * \left(\frac{W}{L}\right)^{A_{\mu_0}} * A(L, V_{gs})$$

(19)

$$A(L, V_{gs}) = \left[\frac{V_{gs} - V_T}{V_{aa}}\right]^{\gamma_0^{*}(L)^{s_\gamma}}$$

(20)

In addition, it was found that  $A_{\mu0}$  and  $A_R$  have respectively values of -0.46 and -0.58. With these values, the term  $R(W/L)*\mu_0(W/L)$  wrote:

$$R\left(\frac{W}{L}\right)*\mu_0\left(\frac{W}{L}\right) = R_{scal}*\mu_{scal}*\left(\frac{W}{L}\right)^{-1,04}$$

(21)

Generally, the mobility is intrinsic to the materials and to the device structure. This is the case for MOS crystalline devices, i.e., there is no geometry dependence of the mobility. But for OTFTs, as proved in this work the mobility have a geometry dependence. Indeed, as explained in [24], for higher W, the band mobility decreases due to an increasing number of defects and traps over the larger area within the channel or due to their round geometry which impacts the mobility. In addition, due to the series resistance effects impacting the current for small channel lengths, the band mobility increased with greater L. These two effects help understanding the found dependence of band mobility with small ratios of W/L showing higher mobility. The original Amorphous-Si: H TFT model in above-threshold regime was then modified accordingly, to be usable with OTFTs following (22) and (26).

$$I_{ds} = \frac{\left(\frac{W}{L}\right) * \left(\frac{W}{L}\right)^{-0.46} Cst_{1}(L)}{1 + \left(\frac{W}{L}\right) * \left(\frac{W}{L}\right)^{-1.04} * Cst_{2}(L)}$$

(22)

$$Cst_{1}'(L) = C_{ox} * \mu_{scal} * A(L, V_{gs}) * (1 + \lambda_{0} * (L)^{B_{\lambda}} * V_{ds}) * (V_{gs} - V_{T}) \frac{V_{ds}}{\left[1 + \left(\frac{V_{ds}}{V_{dsSat}(L)}\right)^{M}\right]^{1/M}}$$

(23)

$$Cst_{2}(L) = C_{ox} * \mu_{scal} * R_{scal} * A(L, V_{gs}) * (V_{gs} - V_{T})$$

(24)

$$V_{dsSat}(L) = \alpha_0 * (L)^{B_{\alpha}} * (V_{gs} - V_T)$$

(25)

$$I_{ds} \approx \sqrt{\frac{W}{L}} * \frac{Cst_1(L)}{\left(1 + Cst_2(L)\right)}$$

(26)

## 5. Model validation

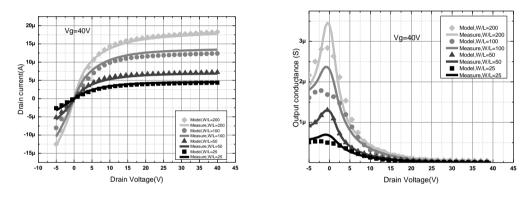

Thanks to (26), the currents appeared to present a specific geometry dependence. For the model validation, two steps are presented. Firstly, the measured curves are compared with modelled ones for different geometries. Secondly, the model is tested with basic circuits.

## F. Series resistance

In Fig.9, the modelled dependences of series resistance on gate-source voltage for different drain-source voltages are represented. Although in literature, series resistance are L-dependent [25]–[27], the W/L-dependence found here respected the series-resistance dependence on gate-source voltages.

Figure 9. Modelled series resistance of the proposed model, Acene-based diimide N-OTFT, W/L=1000  $\mu$ m/20 $\mu$ m, T=25°C

# G. Model performance

Using the proposed model, modelled curves for different geometries to validate the scalability were compared to measured ones as shown in Fig.10 and in Fig.11.

Figure 10. Modelled (dotted) and measured (lines) characteristics for different geometries of Acene-based diimide N-OTFT, Vds=40V, T°=25°C

Figure 11. Modelled (dotted) and measured (lines) characteristics for different geometries of Acene-based diimide N-OTFT, Vgs=40V, T°=25°C

The comparison between modelled characteristics and measured ones for different geometries showed correct performance. The presented results for validation were obtained by considering the average measurements of OTFTs with same dimensions. Indeed, there is a non-negligible scattering on the manufacturing process as related in [28].

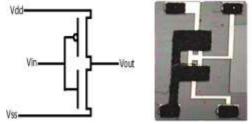

#### H. Model test with basic CMOS circuits

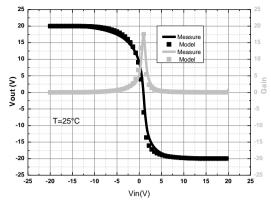

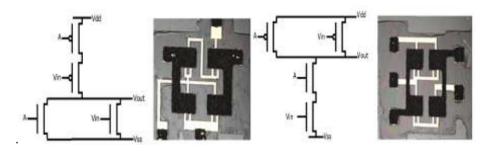

The last step validation was to test the model with basic circuits. The model was therefore tested with inverters, NAND and NOR logic circuits. P-type modeling were done separately and independently to the N-Type one but followed the same procedure. Designed organic inverters were made from P-OTFT having dimensions of W/L=25 and N-OTFT having dimensions W/L=50. The schematic and the corresponding picture of one organic inverter are represented in Fig.12. N transistors were twice as big as P one to compensate the mobility difference between holes and electrons. Indeed, extracted mobilities were twice as high for the holes as for the electrons. The compensation permitted to equilibrate inverter with nearly no offset. A high DC gain of 18 both for measurement and simulation was found under a +/-20V supply as shown in Fig. 13.

Figure 12. Schematic and picture of a designed organic inverter

Figure 13. Modelled and measured performances of one designed 1-2 organic inverter

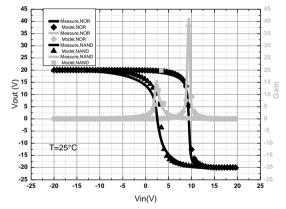

After a validation with a two-transistor circuit, the model was tested with NAND and NOR circuits as represented in Fig.14. Only the inverter function was checked. The circuits were made with N-and P-OTFTs having the same W/L ratios of 50. This, caused an offset to the right due the difference between N- and P-type mobilities. This offset was taken into account by the proposed model as observed in Fig.15.

Figure 14. Schematics and pictures of a designed organic NOR (left) and a designed organic NAND (right)

Figure 15 showed that the model was able to predict offsets and gain values found in measurements both for NOR and NAND circuits confirming the correct performance of the proposed model.

Figure 15. Modelled and measured performances of a designed organic NAND and a designed organic NOR

# 6. CONCLUSION

This work shows once again the possible use of Amorphous-Si: H TFT model for OTFTs modeling. The new contribution of this work is the improved extraction method applicable to any OTFTs without regards to the geometries, materials or manufacturing process. Another contribution is the geometry dependences of extracted parameters, at the same time permitting to adapt the original model for OTFTs and allowing the creation of a single model for different geometries. Table 2 summarizes the model performance and shows the effort done in series-resistance modeling and in circuit validations compared with others works. At the moment, the presented model includes the static part at ambient temperature. In future works, temperature and dynamic parts will be inserted.

|                                 | [17]        | [29]     | [This work]             |

|---------------------------------|-------------|----------|-------------------------|

| Model card(s)                   | Several     | Several  | Single                  |

| Current derivatives validations | No          | No       | Included                |

| Validation with basic circuits  | No          | Included | Included                |

| Series resistance modeling      | No          | Included | Included                |

| Model                           | A-Si: H TFT | VRH      | Modified<br>A-Si: H TFT |

## Table 2: Benchmarking of the proposed model with literature

#### REFERENCES

- [1] S. Jacob, M. Benwadih, *et al*, "High performance printed N and P-type OTFTs for CMOS applications on plastic substrate," *Solid-State Electronics*, Volume 84, June 2013, Pages 167-178, ISSN 0038-1101.

- [2] L. Liu and G. Li, "Modeling and simulation of organic solar cells," 2010 IEEE Nanotechnol. Mater. Devices Conf., pp. 334–338, Oct. 2010.

- [3] M. Estrada, I. Mejía, a. Cerdeira, J. Pallares, L. F. Marsal, and B. Iñiguez, "Mobility model for compact device modeling of OTFTs made with different materials," *Solid. State. Electron.*, vol. 52, no. 5, pp. 787–794, May 2008.

- [4] C. D. Dimitrakopoulos and P. R. L. Malenfant, "Organic Thin Film Transistors for Large Area Electronics," *Adv. Mater.*, vol. 14, no. 2, pp. 99–117, Jan. 2002.

- [5] M. Fadlallah, W. Benzarti, G. Billiot, W. Eccleston, and D. Barclay, "Modeling and characterization of organic thin film transistors for circuit design," *J. Appl. Phys.*, vol. 99, no. 10, p. 104504, 2006.

- [6] P. V. Necliudov, M. S. Shur, D. J. Gundlach, and T. N. Jackson, "Modeling of organic thin film transistors of different designs," J. Appl. Phys., vol. 88, no. 11, p. 6594, 2000.

- [7] A. K. Agarwal and B. Mazhari, "Simultaneous extraction of source and drain resistances in top contact organic thin film transistors from a single test structure," Org. Electron., vol. 13, no. 11, pp. 2659–2666, 2012.

- [8] H. Klauk, M. Halik, U. Zschieschang, F. Eder, D. Rohde, G. Schmid, and C. Dehm, "Flexible Organic Complementary Circuits," *IEEE Trans. Electron Devices*, vol. 52, no. 4, pp. 618–622, Apr. 2005.

- [9] D. M. de Leeuw and E. Cantatore, "Organic electronics: Materials, technology and circuit design developments enabling new applications," *Mater. Sci. Semicond. Process.*, vol. 11, no. 5–6, pp. 199–204, Oct. 2008.

- [10] M. Guerin, A. Daami, et al, "High gain fully printed organic complementary circuits on flexible plastic foils.", Electron Devices, IEEE Transactions, vol.58, no.10, pp.3587,3593, Oct. 2011

- [11] R. Brown, C. P. Jarrett, D. M. de Leeuw, and M. Matters, "Field-effect transistors made from solution-processed organic semiconductors," *Synth. Met.*, vol. 88, no. 1, pp. 37–55, Apr. 1997.

- [12] K. Fukuda, T. Sekine, Y. Kobayashi, Y. Takeda, and M. Shimizu, "Organic integrated circuits using room-temperature sintered silver nanoparticles as printed electrodes," Org. Electron., vol. 13, no. 12, pp. 3296–3301, 2012.

- [13] S. Abdinia, M. Benwadih, R. Coppard, S. Jacob, L. Maddiona, G. Maiellaro, L. Mariucci, and M. Rapisarda, "Design of Analog and Digital Building Blocks in a Fully Printed Complementary Organic Technology," *ESSCIRC*, 2012 Proceedings of the, vol., no., pp.145,148, 17-21 Sept. 2012.

- [14] S. Abdinia, M. Benwadih, et al, "A 4-bit ADC Manufactured in a Fully-Printed Organic Complementary Technology Including Resistors.", Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International, vol., no., pp.106,107, 17-21 Feb. 2013

- [15] V. Fiore, E. Ragonese, S. Abdinia, S. Jacob, I. Chartier, R. Coppard, A. van Roermund, E. Cantatore, and G. Palmisano, "30.4 A 13.56MHz RFID tag with active envelope detection in an organic complementary TFT technology," 2014 IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap., pp. 492–493, Feb. 2014.

- [16] M. Estrada, "Accurate modeling and parameter extraction method for organic TFTs," *Solid-state Electronics*, vol. 49, no. 6, pp. 1009-1016, 2005.

- [17] O. Yaghmazadeh, Y. Bonnassieux, A. Saboundji, L. Cnrs-umr, E. Polytechnique, B. Geffroy, D. Tondelier, and G. Horowitz, "A SPICE-like DC Model for Organic Thin-Film Transistors," *Journal of the Korean Physical Society*, Vol. 54, No. 1, January 2009, pp. 523526.

- [18] B. In, R. Picos, D. Veksler, A. Koudymov, M. S. Shur, T. Ytterdal, and W. Jackson, "Universal compact model for longand short-channel Thin-Film Transistors," *Solid-State Electronics*, vol. 52, pp. 400–405, 2008.

- [19] A. Cerdeira, M. Estrada, R. Garc, and A. Ortiz-conde, "New procedure for the extraction of basic a-Si : H TFT model parameters in the linear and saturation regions," *Solid-State Electronic*, vol. 45, pp. 1077–1080, 2001.

- [20] L. Reséndiz, M. Estrada, and a. Cerdeira, "New procedure for the extraction of a-Si:H TFTs model parameters in the subthreshold region," *Solid. State. Electron.*, vol. 47, no. 8, pp. 1351–1358, Aug. 2003.

- [21] M. Estrada , A. Cerdeira , A. Ortiz-Conde , F.J. Garcia Sanchez ,B. Iniguez , "Extraction method for polycrystalline TFT above and below threshold model parameters," *Solid. State. Electron*, vol. 46, pp. 2295–2300, 2002.

- [22] C. H. Kim, S. Member, A. Castro-carranza, M. Estrada, S. Member, A. Cerdeira, Y. Bonnassieux, G. Horowitz, and B. Iñiguez, "A Compact Model for Organic Field-Effect Transistors With Improved Output Asymptotic Behaviors," *Electron Devices, IEEE Transactions on*, vol.60, no.3, pp.1136,1141, March 2013.

- [23] J. N. Haddock, X. Zhang, S. Zheng, Q. Zhang, S. R. Marder, and B. Kippelen, "A comprehensive study of short channel effects in organic field-effect transistors," *Org. Electron.*, vol. 7, no. 1, pp. 45–54, Feb. 2006.

- [24] D. Spiehl, S. Pankalla, M. Glesner, and E. Doersam, "Analysis of the mobility of printed organic p-channel transistors depending on the transistor geometry and orientation," *J. Phys. Conf. Ser.*, vol. 345, p. 012013, Feb. 2012.

- [25] G. J. Hu, "Gate-voltage-dependent effective channel length and series resistance of LDD MOSFET's," *IEEE Trans. Electron Devices*, vol. 34, no. 12, pp. 2469–2475, Dec. 1987.

- [26] Tarek Zaki, Reinhold Rödel, Florian Letzkus, Harald Richter, Ute Zschieschang, Hagen Klauk, Joachim N. Burghartz, "AC characterization of organic thin-film transistors with asymmetric gate-to-source and gate-to-drain overlaps ", *Organic Electronics*, Volume 14, Issue 5, May 2013, Pages 1318-1322, ISSN 1566-1199.

- [27] Stéphane Altazin, Raphaël Clerc, Romain Gwoziecki, Damien Boudinet, Gérard Ghibaudo, Georges Pananakakis, Isabelle Chartier, Romain Coppard, "Analytical modeling of the contact resistance in top gate/bottom contacts organic thin film transistors", *Organic Electronics*, Volume 12, Issue 6, June 2011, Pages 897-902, ISSN 1566-1199.

- [28] M. A.Sankhare, M.Guerin, E. Bergeret, P. Pannier, and R. Coppard, "Full-printed otft modeling: impacts of process variation 1,"*ICSICT*, 28-31 Oct. 2014.

- [29] M. Fadlallah, G. Billiot, W. Eccleston, and D. Barclay, "DC/AC unified OTFT compact modeling and circuit design for RFID applications," *Solid. State. Electron.*, vol. 51, no. 7, pp. 1047–1051, Jul. 2007.